- 您现在的位置:买卖IC网 > Sheet目录307 > ADE7758ARWZRL (Analog Devices Inc)IC ENERGY METERING 3PHASE 24SOIC

�� �

�

�

�Data� Sheet�

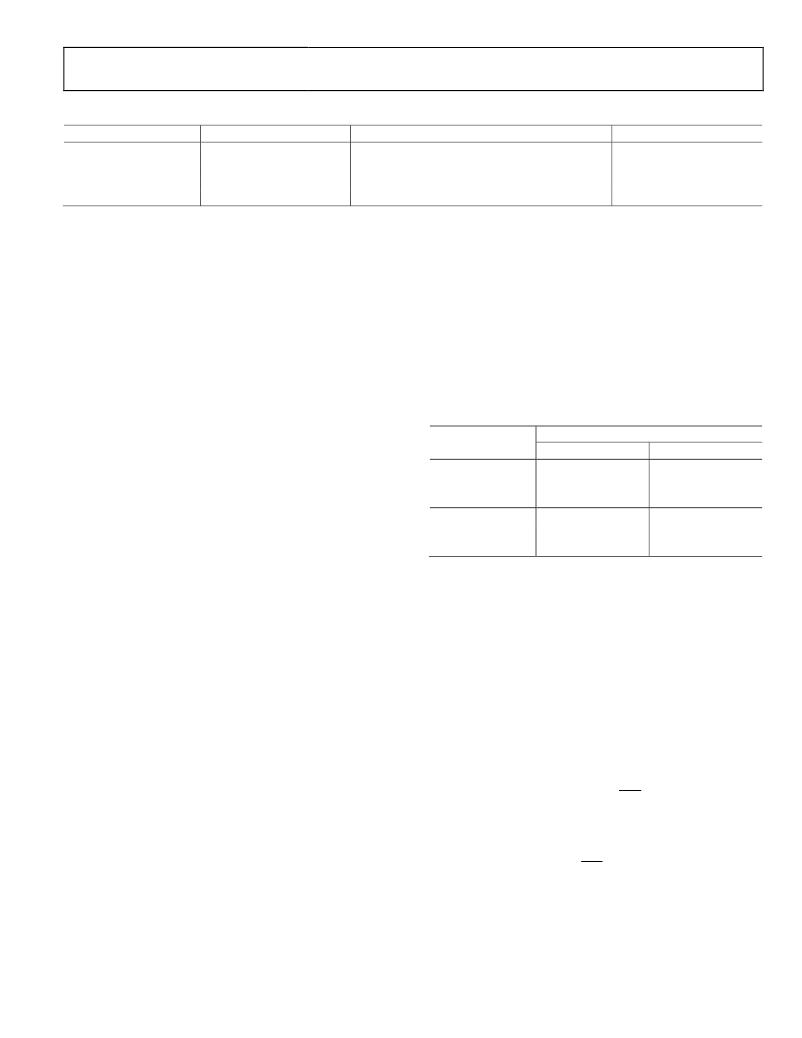

�Table� 14.� Inputs� to� VA-Hr� Accumulation� Registers�

�ADE7758�

�CONSEL[1,� 0]�

�00�

�01�

�10�

�11�

�AVAHR� 1�

�AVRMS� � AIRMS�

�AVRMS� � AIRMS�

�AVRMS� � AIRMS�

�Reserved�

�BVAHR�

�BVRMS� � BIRMS�

�AVRMS� +� CVRMS/2� � BIRMS�

�BVRMS� � BIRMS�

�Reserved�

�CVAHR�

�CVRMS� � CIRMS�

�CVRMS� � CIRMS�

�CVRMS� � CIRMS�

�Reserved�

�1�

�AVRMS/BVRMS/CVRMS� are� the� rms� voltage� waveform,� and� AIRMS/BIRMS/CIRMS� are� the� rms� values� of� the� current� waveform.�

�Energy� Accumulation� Mode�

�The� apparent� power� accumulated� in� each� VA-hr� accumulation�

�register� (AVAHR,� BVAHR,� or� CVAHR)� depends� on� the� con-�

�figuration� of� the� CONSEL� bits� in� the� COMPMODE� register�

�(Bit� 0� and� Bit� 1).� The� different� configurations� are� described� in�

�Table� 14.�

�The� contents� of� the� VA-hr� accumulation� registers� are� affected�

�by� both� the� registers� for� rms� voltage� gain� (VRMSGAIN),� as� well�

�as� the� VAGAIN� register� of� the� corresponding� phase.�

�Apparent� Power� Frequency� Output�

�Pin� 17� (VARCF)� of� the� ADE7758� provides� frequency� output� for�

�the� total� apparent� power.� By� setting� the� VACF� bit� (Bit� 7)� of� the�

�root� of� their� sum� to� determine� the� apparent� energy� over� the�

�same� period.�

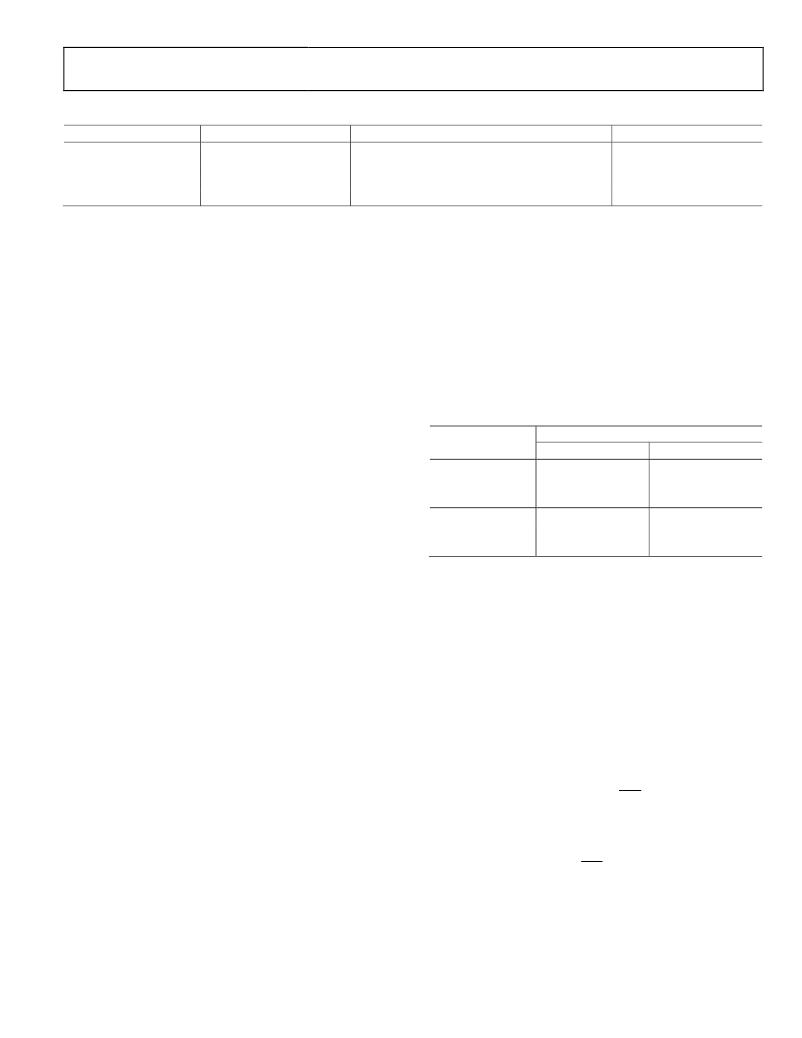

�ENERGY� REGISTERS� SCALING�

�The� ADE7758� provides� measurements� of� active,� reactive,� and�

�apparent� energies� that� use� separate� signal� paths� and� filtering� for�

�calculation.� The� differences� in� the� datapaths� can� result� in� small�

�differences� in� LSB� weight� between� the� active,� reactive,� and�

�apparent� energy� registers.� These� measurements� are� internally�

�compensated� so� that� the� scaling� is� nearly� one� to� one.� The�

�relationship� between� the� registers� is� shown� in� Table� 15.�

�Table� 15.� Energy� Registers� Scaling�

�Frequency�

�WAVMODE� register,� this� pin� provides� an� output� frequency� that�

�is� directly� proportional� to� the� total� apparent� power.�

�Integrator� Off�

�60� Hz�

�50� Hz�

�A� digital-to-frequency� converter� (DFC)� is� used� to� generate� the�

�pulse� output� from� the� total� apparent� power.� The� TERMSEL� bits�

�(Bit� 2� to� Bit� 4)� of� the� COMPMODE� register� can� be� used� to�

�select� which� phases� to� include� in� the� total� power� calculation.�

�Setting� Bit� 2,� Bit� 3,� and� Bit� 4� includes� the� input� to� the� AVAHR,�

�VAR�

�VA�

�Integrator� On�

�VAR�

�VA�

�1.004� � WATT�

�1.00058� � WATT�

�1.0059� � WATT�

�1.00058� � WATT�

�1.0054� � WATT�

�1.0085� � WATT�

�1.0064� � WATT�

�1.00845� � WATT�

�BVAHR,� and� CVAHR� registers� in� the� total� apparent� power�

�calculation.� A� pair� of� frequency� divider� registers,� namely�

�VARCFDEN� and� VARCFNUM,� can� be� used� to� scale� the� output�

�frequency� of� this� pin.� Note� that� either� VAR� or� apparent� power�

�can� be� selected� at� one� time� for� this� frequency� output� (see� the�

�Reactive� Power� Frequency� Output� section).�

�Line� Cycle� Apparent� Energy� Accumulation� Mode�

�The� line� cycle� apparent� energy� accumulation� mode� is� activated�

�by� setting� the� LVA� bit� (Bit� 2)� in� the� LCYCMODE� register.� The�

�total� apparent� energy� accumulated� over� an� integer� number� of�

�zero� crossings� is� written� to� the� VA-hr� accumulation� registers�

�after� the� LINECYC� number� of� zero� crossings� is� detected.� The�

�operation� of� this� mode� is� similar� to� watt-hr� accumulation� (see�

�the� Line� Cycle� Active� Energy� Accumulation� Mode� section).�

�When� using� the� line� cycle� accumulation� mode,� the� RSTREAD�

�bit� (Bit� 6)� of� the� LCYCMODE� register� should� be� set� to� Logic� 0.�

�Note� that� this� mode� is� especially� useful� when� the� user� chooses�

�to� perform� the� apparent� energy� calculation� using� the� vectorial�

�method.�

�By� setting� LWATT� and� LVAR� bits� (Bit� 0� and� Bit� 1)� of� the�

�WAVEFORM� SAMPLING� MODE�

�The� waveform� samples� of� the� current� and� voltage� waveform,� as�

�well� as� the� active,� reactive,� and� apparent� power� multiplier� out-�

�puts,� can� all� be� routed� to� the� WAVEFORM� register� by� setting�

�the� WAVSEL[2:0]� bits� (Bit� 2� to� Bit� 4)� in� the� WAVMODE�

�register.� The� phase� in� which� the� samples� are� routed� is� set� by�

�setting� the� PHSEL[1:0]� bits� (Bit� 0� and� Bit� 1)� in� the� WAVMODE�

�register.� All� energy� calculation� remains� uninterrupted� during�

�waveform� sampling.� Four� output� sample� rates� can� be� chosen� by�

�using� Bit� 5� and� Bit� 6� of� the� WAVMODE� register� (DTRT[1:0]).�

�The� output� sample� rate� can� be� 26.04� kSPS,� 13.02� kSPS,�

�6.51� kSPS,� or� 3.25� kSPS� (see� Table� 20).�

�By� setting� the� WFSM� bit� in� the� interrupt� mask� register� to�

�Logic� 1,� the� interrupt� request� output� IRQ� goes� active� low� when�

�a� sample� is� available.� The� 24-bit� waveform� samples� are�

�transferred� from� the� ADE7758� one� byte� (8� bits)� at� a� time,� with�

�the� most� significant� byte� shifted� out� first.�

�The� interrupt� request� output� IRQ� stays� low� until� the� interrupt�

�routine� reads� the� reset� status� register� (see� the� Interrupts� section).�

�LCYCMODE� register,� the� active� and� reactive� energies� are�

�accumulated� over� the� same� period.� Therefore,� the� MCU� can�

�perform� the� squaring� of� the� two� terms� and� then� take� the� square�

�Rev.� E� |� Page� 41� of� 72�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ADE7761AARSZ-RL

IC ENERGY METERING 1PHASE 20SSOP

ADE7761BARSZ-RL

IC ENERGY METERING 1PHASE 20SSOP

ADE7768ARZ-RL

IC ENERGY METERING 1PHASE 16SOIC

ADE7769ARZ-RL

IC ENERGY METERING 1PHASE 16SOIC

ADM8843ACPZ-REEL7

IC LED DRVR WHITE BCKLGT 16LFCSP

ADP1653ACPZ-R7

IC LED DRVR PHOTO FLASH 16-LFCSP

ADP1712-EVALZ

BOARD EVALUATION ADP1712

ADP1720-EVALZ

BOARD EVAL FOR ADP1720-ADJ

相关代理商/技术参数

ADE7759

制造商:AD 制造商全称:Analog Devices 功能描述:Active Energy Metering IC with di/dt Sensor Interface

ADE7759ARS

功能描述:IC ENERGY METERING 1PHASE 20SSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 能量测量 系列:- 产品培训模块:Lead (SnPb) Finish for COTS

Obsolescence Mitigation Program 标准包装:2,500 系列:*

ADE7759ARSRL

功能描述:IC ENERGY METERING 1PHASE 20SSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 能量测量 系列:- 产品培训模块:Lead (SnPb) Finish for COTS

Obsolescence Mitigation Program 标准包装:2,500 系列:*

ADE7759ARSZ

功能描述:IC ENERGY METERING 1PHASE 20SSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 能量测量 系列:- 产品培训模块:Lead (SnPb) Finish for COTS

Obsolescence Mitigation Program 标准包装:2,500 系列:*

ADE7759ARSZRL

功能描述:IC ENERGY METERING 1PHASE 20SSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 能量测量 系列:- 产品培训模块:Lead (SnPb) Finish for COTS

Obsolescence Mitigation Program 标准包装:2,500 系列:*

ADE7760

制造商:AD 制造商全称:Analog Devices 功能描述:Energy Metering IC with On-Chip Fault Detection

ADE7760ARS

制造商:Analog Devices 功能描述:Energy Measurement 20-Pin SSOP 制造商:Analog Devices 功能描述:ENERGY METER IC W/ ONCHIP FAULT & OSCIL. - Rail/Tube

ADE7760ARSRL

制造商:Analog Devices 功能描述:Energy Measurement 20-Pin SSOP T/R 制造商:Analog Devices 功能描述:ENERGY METER IC W/ONCHIP FAULT & OSCIL. - Tape and Reel